# Ver: 1.05

# **Register Mapping**

# **Specification**

**CAL207**

Ver: 1.05

# HERCROM400G2 CALYPSO

**Department:** European Wireless Terminal Chipset Business Unit

|      | Originator     |

|------|----------------|

| Name | Michel Gac     |

| Date | 2 – May – 2000 |

# **HISTORY**

| Version | Date         | Author     | Approval manager | Approval date | Notes |

|---------|--------------|------------|------------------|---------------|-------|

| 0.1     | 02-May-2000  | Michel Gac | manager          | date          | 1     |

| 0.2     | 27-Jun-2000  | Michel Gac |                  |               | 2,3   |

|         |              | Michel Gac |                  |               | 4     |

| 0.3     | 10-Aug-2000  |            |                  |               | ·     |

| 0.4     | 05-Sep-2000  | Michel Gac |                  |               | 5     |

| 0.5     | 23-Sep-2000  | Michel Gac |                  |               | 6     |

| 0.6     | 11-Dec-2000  | R. Servato | Michel Gac       | 12-Dec-2000   | 7     |

| 0.7     | 15-Dec-2000  | R. Servato | Michel Gac       | 18-Dec-2000   | 8     |

| 8.0     | 15-Feb-2001  | R. Servato | Michel Gac       | 16-Feb-2001   | 9     |

| 0.9     | 26-Mar-2001  | R. Servato | Michel Gac       | 27-Mar-2001   | 10    |

| 0.91    | 1-June-2001  | R. Servato | Michel Gac       | 1-June-2001   | 11    |

| 0.92    | 18-June-2001 | R. Servato | Michel Gac       | 23-July-2001  | 12    |

| 0.93    | 20-Aug-2001  | R. Servato | Michel Gac       | 22-Augt-2001  | 13    |

| 0.94    | 27-sept-2001 | R. Servato | Michel Gac       | 11-Oct-2001   | 14    |

| 0.95    | 22-oct-2001  | R. Servato | Michel Gac       | 22-Oct-2001   | 15    |

| 1.00    | 24-oct-2001  | R. Servato | Michel Gac       | 14-Nov-2001   | 16    |

| 1.01    | 28-Nov-2001  | R. Servato | Michel Gac       | 28-Nov-2001   | 17    |

| 1.02    | 28-Jun-2001  | R. Servato | Michel Gac       | 12-July-2001  | 18    |

| 1.03    | 15-Oct-2002  | R. Servato | Michel Gac       | 15-Oct-2002   | 19    |

| 1.04    | 16-Dec-2002  | R. Servato | Michel Gac       | 16-Dec-2002   | 20    |

| 1.05    | 5-May-2003   | R. Servato | Michel Gac       | 5-May-2003    | 21    |

## **NOTES**

- 1. Imported from SAM207.

- 2. Updated MCU memory mapping.

- 3. Updated MCU Rhea strobe 0,1 mapping.

- 4. Fix bug in MPU mapping table.

- 5. Update RTC registers.

- 6. Update MCU IRQ mapping

- 7. Preliminary update for Calypso

- 8. Update UART interrupt (Irq 7/18), UART registers (SSR, IIR, SFLSR, BLR)

- Update DPLL register (PLL\_MULT),RIF Register (SPCX), MCU memory map (Table 2 : API RAM)

- 10. Update Device version code, DSP configuration (Bit 8), Change active edge of serial clock for UWIRE register (cso\_edge\_rd, cso\_edge\_wr)

- 11. Update MPU (Ch 5.8, 5.10, 5.11).

- 12. Add Rhea peripheral latency (Ch 17.6). remove reference document Ch.

- 13. update Ch 17.2 (reset value for ACCESS\_FACTOR1), update MCU peripheral mapping Table 4 (remove Osc32K), Add Ch 28.6.1 (Current resistance value for OSC32K), update Ch 8.3 (reset value for TIMEOUT), update Ch 21.3/21.4 (reset value), update Ch 33.10.2 (reset value for RX\_FIFO\_E).

- 14. Update MPU Chap, update MCU peripheral mapping table

- 15. Update GAUGING\_CTRL\_REG register (ch 29.4.1)

**PAGE: 2/178**

- Ver: 1.05

- 16. Update DieID code (Ch7.6, bit63:47), update Acess\_Factor formula ch17.2, update Maximun latency for each peripherals table(Ch 17.6), add Pheripheral\_Acces\_Freq for peripherals in Ch Rhea\_cntl\_reg (Ch 17.2), complete description of IO\_CNTL\_REG (Ch 24.4), update Ch 11.2.2 (register in can be accessed in supervisor mode only), update ASIC\_CONF\_REG (Bit 6) and MCR reg bit0 (Ch 33.12) Add features for CALYPSO C035: Update Ch 1 (MCU Memory MAP using ADD(22), using CS4), Update Ch 4.5 (MPU description) update Ch 7.2/7.3 (ID code, version code), update Ch 7.9 (Asic Configuration), Update Ch19 (CNTL\_ARM\_DIV reg), update Ch 28.6 (RTC\_RES\_PROG\_REG), modify nota Ch 26.4 (TPU sequencer internal address mapping)

- 17. Update API size to 16K in Chapter MCU memory map using ADD(22) (ch1.2)

- 18. Update reset value for DPLL control reg (PLL\_MULT=0), update GEA programming scheduling chapter (Ch6.17), update UART mode LSR register (bitO = '0' for reset value Ch 33.10.1)

- 19. remove reference to F# (F741xxx, F751xxx instead)

- 20. Update specification for calypsoLite: Update MCU memory mapping, add device IDcode.

- 21. Update Extra control register (Ch 3.10), update maximum latency formula and table (ch 17.6).

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI seems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI-products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Not does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1998, Texas Instruments Incorporated.

Ver: 1.05

# **CONTENTS**

| 1. | MO           | CU MEMORY MAP                                                | 16 |

|----|--------------|--------------------------------------------------------------|----|

|    | 1.1          | MCU MEMORY MAP USING CS4 (DEFAULT)                           | 16 |

|    | 1.2          | MCU MEMORY MAP USING ADD(22)                                 | 17 |

|    | 1.3          | EXTERNAL FLASH/ROM IMAGE                                     | 17 |

|    | 1.4          | MCU RHEA PERIPHERALS MAPPED ON STROBE 0                      |    |

|    | 1.5          | MCU RHEA PERIPHERALS MAPPED ON STROBE 1                      |    |

|    | 1.6          | Data Format                                                  | 20 |

| 2. | DS           | P MEMORY MAP                                                 | 21 |

|    | 2.1          | MEMORY AREAS DEFINITIONS                                     | 21 |

|    | 2.2          | MAPPING DIAGRAM                                              |    |

|    | 2.3          | API                                                          | 22 |

|    | 2.4          | XIO-RHEA                                                     |    |

|    | 2.4.         |                                                              |    |

|    | 2.4.         |                                                              |    |

|    | 2.4.         |                                                              |    |

|    | 2.4.         | .4 External peripherals mapping – I/O Space                  | 23 |

| 3. | AR           | M MEMORY INTERFACE – FFFF:FB00                               | 24 |

|    | 3.1          | MEMORY INTERFACE REGISTER MAPPING                            | 24 |

|    | 3.2          | NCSO MEMORY RANGE (READ / WRITE) – FFFF:FB00                 |    |

|    | 3.3          | NCS1 MEMORY RANGE (READ / WRITE) – FFFF:FB02                 |    |

|    | 3.4          | NCS2 MEMORY RANGE (READ / WRITE) – FFFF:FB04                 | 25 |

|    | 3.5          | NCS3 MEMORY RANGE (READ / WRITE) – FFFF:FB06                 |    |

|    | 3.6          | CS4 MEMORY RANGE (READ / WRITE) – FFFF:FB0A                  |    |

|    | 3.7          | NCS6 INTERNAL MEMORY RANGE (READ / WRITE) – FFFF:FB0C        |    |

|    | 3.8          | NCS7 INTERNAL MEMORY RANGE (READ / WRITE) - FFFF:FB08        |    |

|    | 3.9          | API-RHEA CONTROL REGISTER CTRL (READ / WRITE) – FFFF:FB0E    |    |

|    | 3.10         | EXTRA CONTROL REGISTER CONF (READ / WRITE) – FFFF:FB10       |    |

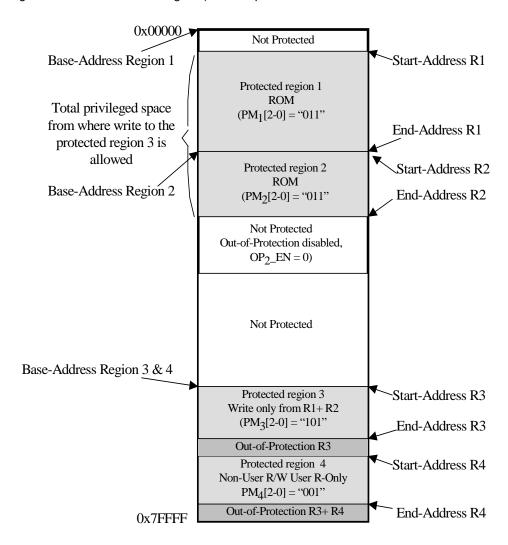

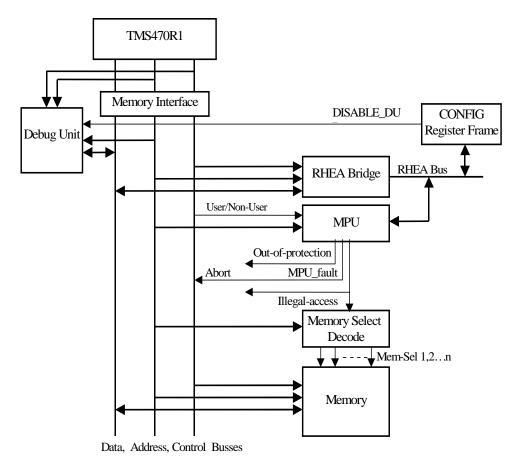

| 4. | ME           | EMORY PROTECTION UNIT (MPU) - FFFF:FF00                      |    |

|    | 4.1          | CONFIGURATION REGISTER MAPPING.                              |    |

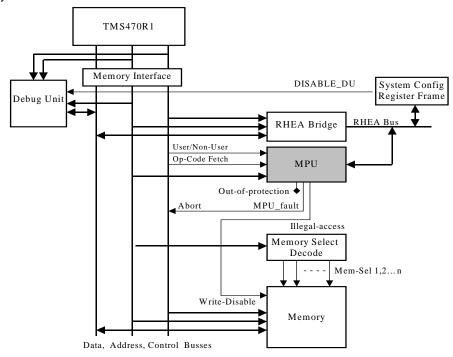

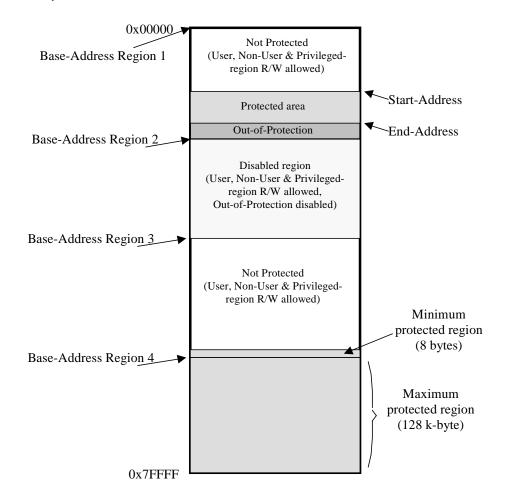

|    | 4.2          | MPU OVERVIEW                                                 |    |

|    | 4.3          | BLOCK DIAGRAM                                                |    |

|    | 4.4          | MPU FEATURE' S                                               |    |

|    | 4.5          | MPU DESCRIPTION                                              |    |

|    | 4.6          | PROTECTION MODE DEFINITION                                   |    |

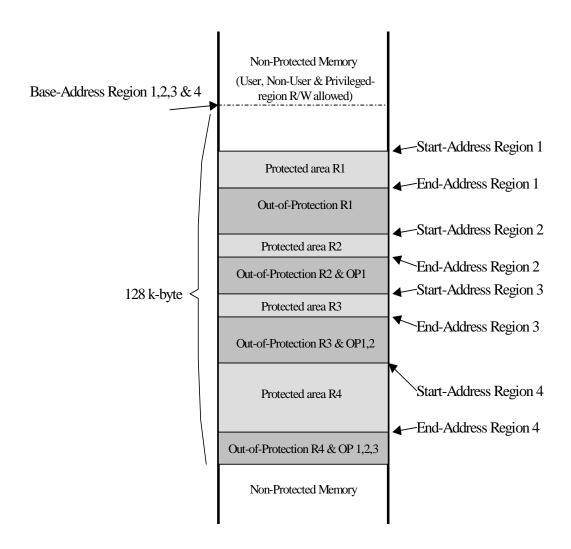

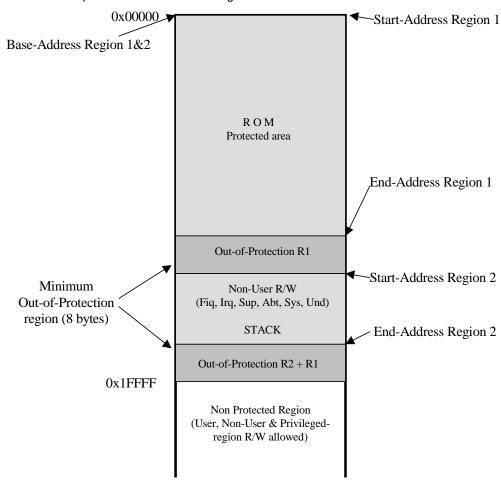

|    | 4.7<br>4.7   | MEMORY PROTECTION EXAMPLE                                    |    |

|    | 4.7.<br>4.7. |                                                              |    |

|    | 4.7.         |                                                              |    |

|    | 4.7.         |                                                              |    |

|    | 4.8          | MPU CONTROL REGISTER FRAME                                   |    |

|    | 4.8.         |                                                              |    |

|    | 4.8          |                                                              |    |

|    | 4.9          | MPU_ST: STATUS REGISTER (READ) – FFFF:FF00                   |    |

|    | 4.10         | MPU_CTL: CONTROL REGISTER (READ / WRITE) – FFFF:FF08         |    |

|    | 4.11         | MPU_PM: PROTECTION MODE REGISTER (READ / WRITE) – FFFF:FF02  |    |

|    | 4.1          |                                                              |    |

|    | 4.1          | 1.2 Protection mode summary                                  | 40 |

|    | 4.12         | MPU_B&STN: BASE & START ADDRESS – REGION N – (READ / WRITE)  | 40 |

|    | 4.13         | MPU_ENDN: END ADDRESS DEFINITION - REGION N - (READ / WRITE) | 40 |

| 5. | DEI          | BUG UNIT (DU) - 03C0:0000                                                  | 4  |

|----|--------------|----------------------------------------------------------------------------|----|

|    | 5.1          | DEBUG UNIT OVERVIEW                                                        | 4  |

|    | 5.2          | DEBUG UNIT FEATURE'S                                                       |    |

|    | 5.3          | DEBUG UNIT DESCRIPTION                                                     | 42 |

|    | 5.4          | DEBUG UNIT ENABLE/DISABLE CONTROL                                          | 43 |

|    | 5.5          | DEBUG-DATA ORGANIZATION                                                    | 44 |

|    | 5.6          | RECORDED DATA EXAMPLES                                                     |    |

|    | 5.7          | DEBUG UNIT MEMORY MAP (03C0:0000)                                          | 45 |

| 6. | GPI          | RS ENCRYPTION ALGORTHYM (GEA1 & 2) - FFFF: C000                            | 40 |

|    | 6.1          | GEA MISCELLANEOUS                                                          | 40 |

|    | 6.2          | LLC overview                                                               |    |

|    | 6.3          | UNACKNOWLEDGED OPERATION                                                   |    |

|    | 6.4          | ACKNOWLEDGED OPERATION                                                     | 4  |

|    | 6.5          | FRAME FORMAT                                                               | 4  |

|    | 6.5.         |                                                                            |    |

|    | 6.5.2        | - T                                                                        |    |

|    | 6.5          | - J                                                                        |    |

|    | 6.5.4        | - 3                                                                        |    |

|    | 6.6          | MEMORY MANAGEMENT                                                          |    |

|    | 6.7          | GEA REGISTER MAPPING                                                       |    |

|    | 6.8          | CONTROL REGISTER: CNTL_REG (READ / WRITE) – FFFF: C000.                    |    |

|    | 6.9          | STATUS REGISTER: STATUS_REG (READ) – FFFF: C002                            |    |

|    | 6.10<br>6.11 | UPLINK CONFIGURATION REGISTERS: CONF_UL_REG(1:5)                           |    |

|    | 6.11         | , ,                                                                        |    |

|    | 6.11         | ,                                                                          |    |

|    | 6.11         |                                                                            |    |

|    | 6.11         | ,                                                                          |    |

|    | 6.11         |                                                                            |    |

|    | 6.11         | • • • • • • • • • • • • • • • • • • • •                                    |    |

|    | 6.12         | , ,                                                                        |    |

|    | 6.12         | 2.1 Downlink register 1: CONF_DL_REG1 (Read / Write) – FFFF:C010           | 54 |

|    | 6.12         |                                                                            |    |

|    | 6.12         |                                                                            |    |

|    | 6.12         |                                                                            |    |

|    | 6.12         | =                                                                          |    |

|    | 6.12         |                                                                            |    |

|    | 6.13         | CIPHERING KEY REGISTERS: KC_REG(1:4) (READ / WRITE) – FFFF: C01A           |    |

|    | 6.14         | FCS UPLINK REGISTERS: FCS_UL_REG(1:2) - FFFF: C022 / C024                  |    |

|    | 6.15<br>6.16 | FCS DOWNLINK REGISTERS: FCS_DL_REG(1:2) – FFFF:C026 / C028  DATA REGISTERS |    |

|    | 6.16         |                                                                            |    |

|    | 6.16         |                                                                            |    |

|    | 6.16         |                                                                            |    |

|    | 6.16         |                                                                            |    |

|    | 6.17         | GEA PROGRAMMING SCHEDULING                                                 |    |

| 7. | COI          | NFIGURATION REGISTERS - FFFE:F000                                          |    |

| •  | 7.1          | CONFIGURATION REGISTER MAPPING                                             |    |

|    | 7.1          | DEVICE ID CODE (READ ONLY) – FFFE:F000                                     |    |

|    | 7.2          | DEVICE ID CODE (READ ONLY) – FTTE:F000                                     |    |

|    | 7.4          | CDSP ID CODE (READ ONLY) – FFFF:FE02                                       |    |

|    | 7.5          | ARM ID CODE (READ ONLY) – FFFF: FE00.                                      |    |

|    | 7.6          | DIE IDENTIFICATION CODE (READ ONLY) – FFFE:F010 F016                       |    |

|    |              |                                                                            |    |

| 7.7 D            | SP CONFIGURATION (READ / WRITE) – FFFE:F004              | 61 |

|------------------|----------------------------------------------------------|----|

| 7.8 E            | XTENDED MCU CONFIGURATION (READ / WRITE) – FFFE:F006     | 61 |

| 7.9 A            | SIC CONFIGURATION (READ / WRITE) – FFFE:F008             | 62 |

| 7.10 I           | O SELECTION (READ / WRITE) – FFFE:F00A                   | 63 |

| 7.11 N           | ACU SOFTWARE TRACE (READ / WRITE) – FFFE:F00E            | 63 |

| 8. DSP 2         | XIO TO RHEA - XIO:F800                                   | 64 |

| 8.1 X            | IO-RHEA REGISTER MAPPING                                 | 64 |

| 8.2 T            | RANSFER_RATE (READ / WRITE) - XIO:F800                   | 64 |

|                  | RIDGE_CNTL (READ / WRITE) - XIO:F801                     |    |

|                  | EGISTERS - XIO:F900 – FFE0:0000                          |    |

| 9.1 E            | OSP API CONFIGURATION REGISTER MAPPING                   | 66 |

|                  | PIC CONTROL REGISTER                                     |    |

| 9.2.1            | MCU reads from APIC                                      |    |

| 9.2.2            | MCU writes to APIC.                                      |    |

| 9.2.3            | DSP accesses from/to APIC.                               |    |

|                  | A MAPPING                                                |    |

| 10. DIV          | A WAFFING                                                | 0> |

| 11. DM           | A CONTROLLER - FFFF:FC00 - XIO:FC00                      | 70 |

| 11.1 E           | MA REGISTER MAPPING                                      | 70 |

| 11.2 N           | 1CU registers                                            | 71 |

| 11.2.1           | CONTROLLER_CONFIG* (Read / Write) - FFFF:FC00 - XIO:FC00 | 71 |

| 11.2.2           | ALLOC_CONFIG* (Read / Write) - FFFF:FC02 - XIO:FC02      | 71 |

| 11.3 E           | MA CHANNEL 1 CONFIGURATION REGISTERS – FFFF:FC10         | 72 |

| 11.3.1           | DMA1_RAD (Read / Write) - FFFF:FC10 - XIO:FC10           | 72 |

| 11.3.2           | _ (                                                      |    |

| 11.3.3           | _ (                                                      |    |

| 11.3.4           | = - ( ,                                                  |    |

| 11.3.5           | =- ( ,                                                   |    |

| 11.3.6           |                                                          |    |

|                  | MA CHANNEL 2 CONFIGURATION REGISTERS – FFFF:FC20         |    |

| 11.4.1           | _                                                        |    |

| 11.4.2           | _ (                                                      |    |

| 11.4.3           |                                                          |    |

| 11.4.4           | = - ( ,                                                  |    |

| 11.4.5           | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                    |    |

| 11.4.6           | ()                                                       |    |

|                  | MA CHANNEL 3 CONFIGURATION REGISTERS – FFFF:FC30         |    |

| 11.5.1           |                                                          |    |

| 11.5.2           |                                                          |    |

| 11.5.3<br>11.5.4 | _                                                        |    |

|                  |                                                          |    |

| 11.5.5<br>11.5.6 |                                                          |    |

|                  | DMAS_CUK_OFFSE1_AF1 (Redd) = FFFF:FC3A = A10:FC3A        |    |

| 11.6.1           |                                                          |    |

| 11.6.1           |                                                          |    |

| 11.6.3           |                                                          |    |

| 11.6.4           |                                                          |    |

| 11.6.5           | _ ,                                                      |    |

| 11.6.6           |                                                          |    |

| 12. RII          | FREGISTERS - FFFF:7000 - XIO:0000                        |    |

|                  | IF REGISTER MAPPING                                      |    |

| 1∠.1 K           | ALENDARD BY MATTING                                      |    |

| Transmit Data Register (DXR) – FFFF:7000 - XIO:0000  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| · /                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| · · · · · · · · · · · · · · · · · · ·                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CONTROL REGISTER (SPCR) – XIO:0003                   | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CYPHER REGISTERS - XIO:2800                          | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CYPHER REGISTER MAPPING                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ·                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| •                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PREDEFINED ORDER IN CASE OF IDENTICAL PRIORITY LEVEL |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ARM7 TO RHEA – FFFF:F900                             | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| /                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ENHANCED_RHEA_CNTL (READ / WRITE) - FFFF:F906        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MAXIMUM LATENCY FOR EACH PERIPHERALS                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      | RECEIVE DATA REGISTER (XSR AND RSR)  SHIFT DATA REGISTER (SEX) — XIO:0002  CONTROL REGISTER (SPCX) — XIO:0003  CYPHER REGISTER (SPCX) — XIO:0003  CYPHER REGISTER (SPCR) — XIO:2800  CYPHER REGISTER S — XIO:2800  CYPHER REGISTER MAPPING  CONTROL REGISTER (CNTL_REG) — XIO:2800  INTERRUPT STATUS REGISTER (STATUS , INC, REG) — XIO:2801  WORKING STATUS REGISTER (STATUS , INC, REG) — XIO:2801  WORKING STATUS REGISTER (STATUS , INC, REG) — XIO:2802  KC REGISTERS I TO 4 (KC_REG#) — XIO:2803 . 2806  COUNT REGISTERS I AND 2 (COUNT, REG#) — XIO:2807 . 2808  DECIPHER DATA REGISTERS I TO 8 (DECL_REG_#) XIO 2809 . 2810  ENCIPHER DATA REGISTERS I TO 8 (ENCL_REG_#) — XIO:2801 . 2818  MCSI REGISTERS — XIO:0800  MCSI REGISTERS — XIO:0800 |

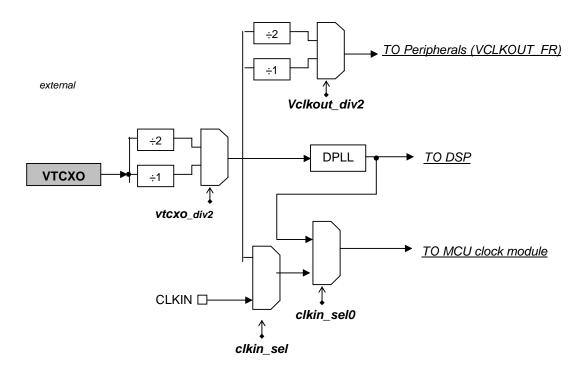

| 18.        | DPLL REGISTER - FFFF:9800                                                       | 101 |

|------------|---------------------------------------------------------------------------------|-----|

| 18.        | 1 DPLL register mapping                                                         | 101 |

| 18.        |                                                                                 |     |

| 1          | 18.2.1 BYPASS mode                                                              | 10  |

| 1          | 18.2.2 LOCK mode                                                                | 10  |

| 1          | 18.2.3 Lock times                                                               | 10  |

| 1          | 18.2.4 Control register access                                                  | 10  |

| 18.        | 3 DPLL CONTROL REGISTER (READ / WRITE) – FFFF:9800                              | 102 |

| 19.        | CLKM REGISTERS - FFFF:FD00                                                      | 103 |

| 19.        | 1 CLKM registers mapping                                                        | 103 |

| 19.        |                                                                                 |     |

| 19.        |                                                                                 |     |

| 19.        | ` / ` /                                                                         |     |

| 19.        |                                                                                 |     |

| 19.        |                                                                                 |     |

| 20.        | TIMER REGISTERS - FFFE:3800 / FFFE:6800                                         | 108 |

|            |                                                                                 |     |

| 20.        |                                                                                 |     |

| 20.        |                                                                                 |     |

| 20.        | ` _ / ` /                                                                       |     |

| 20.<br>20. | $\cdot$ |     |

| 20.        |                                                                                 |     |

| 20.        | $\cdot$ |     |

|            | , – , , , ,                                                                     |     |

| 21.        | WATCHDOG TIMER REGISTERS - FFFF:F800                                            | 110 |

| 21.        | 1 WATCHDOG REGISTERS MAPPING                                                    | 110 |

| 21.        | 2 CONTROL (WATCHDOG_CNTL_TIM) (READ / WRITE) - FFFF:F800                        | 110 |

| 21.        | 3 LOAD TIMER (WATCHDOG_LOAD_TIM) (WRITE) - FFFF:F802                            | 110 |

| 21.        |                                                                                 |     |

| 21.        | 5 TIMER MODE (WATCHDOG_TIM_MODE) - FFFF:F804                                    | 110 |

| 22.        | SPI REGISTERS - FFFE:3000                                                       | 11  |

| 22.        | 1 SPI register mapping                                                          | 111 |

| 22.        |                                                                                 |     |

| 22.        | ` - / ` /                                                                       |     |

| 22.        | 4 CONTROL SPI (REG_CTRL) (READ / WRITE) - FFFE:3004                             | 112 |

| 22.        | 5 STATUS REGISTER (REG_STATUS) (READ) - FFFE:3006                               | 112 |

| 22.        | 6 Transmit registers (REG_TX_LSB/MSB) (Read / Write) - FFFE:3008                | 113 |

| 22.        | 7 RECEIVE REGISTERS (REG_RX_LSB/MSB) (READ) - FFFE:300C                         | 113 |

| 23.        | UWIRE REGISTERS - FFFE:4000                                                     | 114 |

| 23.        | 1 UWIRE register mapping                                                        | 114 |

| 23.        |                                                                                 |     |

| 23.        |                                                                                 |     |

| 23.        |                                                                                 |     |

| 23.        |                                                                                 |     |

| 23.        |                                                                                 |     |

| 23.        |                                                                                 |     |

| 24.        | ARMIO REGISTERS - FFFE:4800                                                     | 118 |

| 24.        | 1 ARMIO REGISTER MAPPING                                                        | 119 |

| 24.        |                                                                                 |     |

| 24.        | , ,                                                                             |     |

|            |                                                                                 |     |

PAGE: 10/178

| 24.4           | INPUT/OUTPUT CONTROL (IO_CNTL_REG) (READ / WRITE) - FFFE:4804                                                                |     |

|----------------|------------------------------------------------------------------------------------------------------------------------------|-----|

| 24.5           | CONTROL ARMIO (ARMIO_CNTL_REG) (READ/WRITE) - FFFE:4806                                                                      |     |

| 24.6           | LOAD TIMER (ARMIO_LOAD_TIM) (READ / WRITE) - FFFE:4808                                                                       |     |

| 24.7           | KEYBOARD ROW INPUTS (KBR_LATCH_REG) (READ) - FFFE:480A                                                                       |     |

| 24.8           | KEYBOARD COLUMN OUTPUTS (KBC_REG) (READ / WRITE) - FFFE:480C                                                                 |     |

| 24.9           | BUZZER & LIGHT CTRL (BUZZ_LIGHT_REG) (READ / WRITE) - FFFE:480E                                                              |     |

| 24.10<br>24.11 | LIGHT POWER LEVEL (LIGHT_LEVEL_REG) (READ / WRITE) - FFFE:4810BUZZER POWER LEVEL (BUZZ_LEVEL_REG) (READ / WRITE) - FFFE:4812 |     |

| 24.11          | GPIO MODE (GPIO_EVENT_MODE_REG) (READ/WRITE) - FFFE:4814                                                                     |     |

| 24.12          | KEYBOARD/GPIO IRQ REGISTER (KBD GPIO INT) (READ) - FFFE:4816                                                                 |     |

| 24.13          | KEYBOARD/GPIO MASK IRQ (KBD_GPIO_MASKIT) (R/W) - FFFE:4818                                                                   |     |

| 24.15          | GPIO DEBOUNCING (GPIO_DEBOUNCING_REG) (R/W) - FFFE:481A                                                                      |     |

| 24.16          | , – , , ,                                                                                                                    |     |

| 24.17          |                                                                                                                              |     |

| 24.            | 17.1 Keyboard connection                                                                                                     |     |

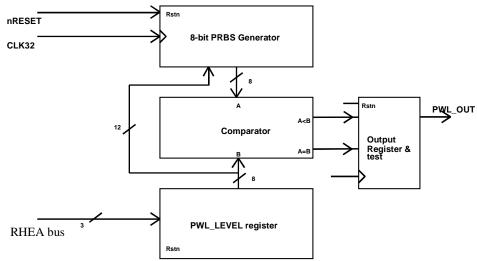

| 24.18          | PULSE WIDTH MODULATION (PWM)                                                                                                 | 122 |

| 24.            | 18.1 Tones creation                                                                                                          | 122 |

| 25. S          | SIM REGISTERS - FFFE:0000                                                                                                    | 123 |

| <b>23.</b> B   |                                                                                                                              |     |

| 25.1           | SIM REGISTER MAPPING                                                                                                         |     |

| 25.2           | REG_SIM_CMD REGISTER (R/W) - FFFE:0000                                                                                       |     |

| 25.3           | REG_SIM_STAT REGISTER (R) - FFFE:0002                                                                                        |     |

| 25.4           | REG_SIM_CONF1 REGISTER (R/W) - FFFE:0004                                                                                     |     |

| 25.5           | REG_SIM_CONF2 REGISTER (R/W) - FFFE:0006                                                                                     |     |

| 25.6<br>25.7   | REG_SIM_IT REGISTER (R) - FFFE:0008                                                                                          |     |

| 25.7           | REG_SIM_DTX REGISTER (R) - FFFE.000C                                                                                         |     |

| 25.9           | REG_SIM_MASKIT REGISTER (R/W) - FFFE:000E                                                                                    |     |

| 25.10          |                                                                                                                              |     |

|                |                                                                                                                              |     |

| 26. T          | SP REGISTERS - FFFE:0800                                                                                                     |     |

| 26.1           | PARALLEL BIT INTERFACE – 0x06 / 0x07                                                                                         |     |

| 26.2           | REG_TSP_ACT_L REGISTER – 0x06                                                                                                |     |

| 26.3           | REG_TSP_ACT_U REGISTER – 0x07                                                                                                |     |

| 26.4           | TPU SEQUENCER INTERNAL ADDRESS MAPPING – 0x00 / 0x11                                                                         |     |

| 26.5           | TSP REGISTER MAPPING                                                                                                         |     |

| 26.6           | TRANSMIT REGISTERS (REG_TX_1/2/3/4) - 0x020x05                                                                               |     |

| 26.7           | RECEIVE REGISTERS (REG_RX_LSB/MSB)- FFFE:0800 0802                                                                           |     |

| 26.7<br>26.7   | -= =                                                                                                                         |     |

| 26.8           | TSP SETUP REGISTERS (REG_TSP_SET1/2/3): 0x09 – 0x0B                                                                          |     |

| 26.8           |                                                                                                                              |     |

| 26.8           |                                                                                                                              |     |

| 26.8           |                                                                                                                              |     |

| 26.9           |                                                                                                                              |     |

| 26.9           | , – – ,                                                                                                                      |     |

| 26.9           |                                                                                                                              |     |

| 26.10          | TSP GAUGING_ENABLE SIGNAL (REG_GAUGING_ENABLE) - 0x11                                                                        | 133 |

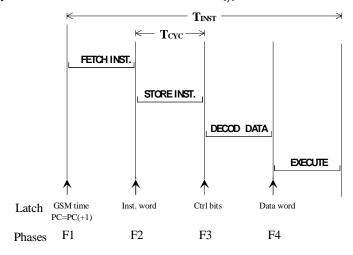

| 27. T          | TPU REGISTERS - FFFF:1000                                                                                                    | 134 |

|                |                                                                                                                              |     |

| 27.1           | TPU REGISTER MAPPING TPU RAM MEMORY MAPPING – FFFF:9000                                                                      |     |

| 27.2<br>27.3   | CONTROL & STATUS REGISTER (REG_TPU_CTRL) (READ / WRITE) - FFFF:1000                                                          |     |

| 27.3           | INTERRUPT STATUS REGISTER (REG_IPU_CTRL) (READ) - FFFF:1004                                                                  |     |

| 27.4           | INTERRUPT STATUS REGISTER (REG_INT_STAT) (READ) - FFFF: 1004                                                                 |     |

| 27.6           | DSP INTERRUPT OCCURRENCE REG. (REG_IT_DSP_PG) (WRITE) - FFFF:1020                                                            |     |

|                |                                                                                                                              |     |

|          | FFSET REGISTER (REG_TPU_OFFSET) (READ) - FFFF:100C   |      |

|----------|------------------------------------------------------|------|

| 27.8 S   | YNCHRO REGISTER (REG_TPU_SYNCHRO) (READ) - FFFF:100E | 137  |

| 27.9 T   | PU-SEQUENCER                                         | 138  |

| 27.9.1   | Functional description                               |      |

| 27.9.2   | Instruction execution flow                           |      |

| 27.9.3   | Micro instructions set definition                    |      |

| 27.9.4   | Structure of the micro-instruction                   | 139  |

| 27.10    | TPU Instruction Set                                  |      |

| 27.10.   | J                                                    |      |

|          | 0.1.1 AT instruction                                 |      |

|          | 0.1.2 OFFSET instruction                             |      |

|          | 0.1.3 SYNCHRO instruction                            |      |

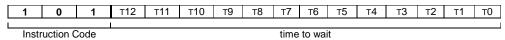

|          | 0.1.4 WAIT instruction                               |      |

| 27.10.2  |                                                      |      |

|          | 0.2.1 MOVE instruction                               |      |

|          |                                                      |      |

| 28. RTC  | C REGISTERS - FFFE:1800                              | 141  |

| 28.1 R   | TC REGISTER MAPPING                                  | 141  |

|          | IME AND CALENDAR REGISTERS (TC) - FFFE:1800 1806     |      |

| 28.2.1   | ` '                                                  |      |

| 28.2.2   | _                                                    |      |

| 28.2.3   | _ , ,                                                |      |

| 28.2.4   |                                                      |      |

| 28.2.5   | _ ,                                                  |      |

| 28.2.6   |                                                      |      |

| 28.2.7   |                                                      |      |

|          | C ALARM REGISTERS - FFFE:1808 180D                   |      |